結局、STAで問題なければよいのでどの記述でもいいわけなんだけど、他にいくつか試してみた。

ケース2と同じ記述でRST_NからRSTを削除したものです。

`default_nettype none

`timescale 1ns/1ps

module fftest5

(

input wire DINX,

input wire CLK,

input wire DIN0,

input wire DIN1,

input wire DIN2,

input wire DIN3,

input wire DIN4,

input wire DIN5,

input wire DIN6,

output reg DOUT

);

reg CLK_DINX;

always @(posedge CLK) begin

CLK_DINX <= DINX;

end

always @(posedge CLK) begin

if(!CLK_DINX) begin

DOUT <= 0;

end else begin

DOUT <= DIN0 | (DIN1 & DIN2 & DIN3 & DIN4 & DIN5 & DIN6);

end

end

endmodule

`default_nettype wire結果はケース2と同じになりました。

0への初期化はリセットと認識されるんですかね?

RST名前もなしに三項演算子で0に初期化するケースです。

`default_nettype none

`timescale 1ns/1ps

module fftest7

(

input wire DINX,

input wire CLK,

input wire DIN0,

input wire DIN1,

input wire DIN2,

input wire DIN3,

input wire DIN4,

input wire DIN5,

input wire DIN6,

output reg DOUT

);

reg CLK_DINX;

always @(posedge CLK) begin

CLK_DINX <= DINX;

end

always @(posedge CLK) begin

DOUT <= (!CLK_DINX)?0:(DIN0 | (DIN1 & DIN2 & DIN3 & DIN4 & DIN5 & DIN6));

end

endmodule

`default_nettype wireこの場合もケース2と同じ結果になった。

0への初期化はRSTとして認識するんですね。

初期化するというよりかいネーブル信号に近い形にしたケースです。

`default_nettype none

`timescale 1ns/1ps

module fftest6

(

input wire DINX,

input wire CLK,

input wire DIN0,

input wire DIN1,

input wire DIN2,

input wire DIN3,

input wire DIN4,

input wire DIN5,

input wire DIN6,

output reg DOUT

);

reg CLK_DINX;

always @(posedge CLK) begin

CLK_DINX <= DINX;

end

always @(posedge CLK) begin

DOUT <= CLK_DINX & (DIN0 | (DIN1 & DIN2 & DIN3 & DIN4 & DIN5 & DIN6));

end

endmodule

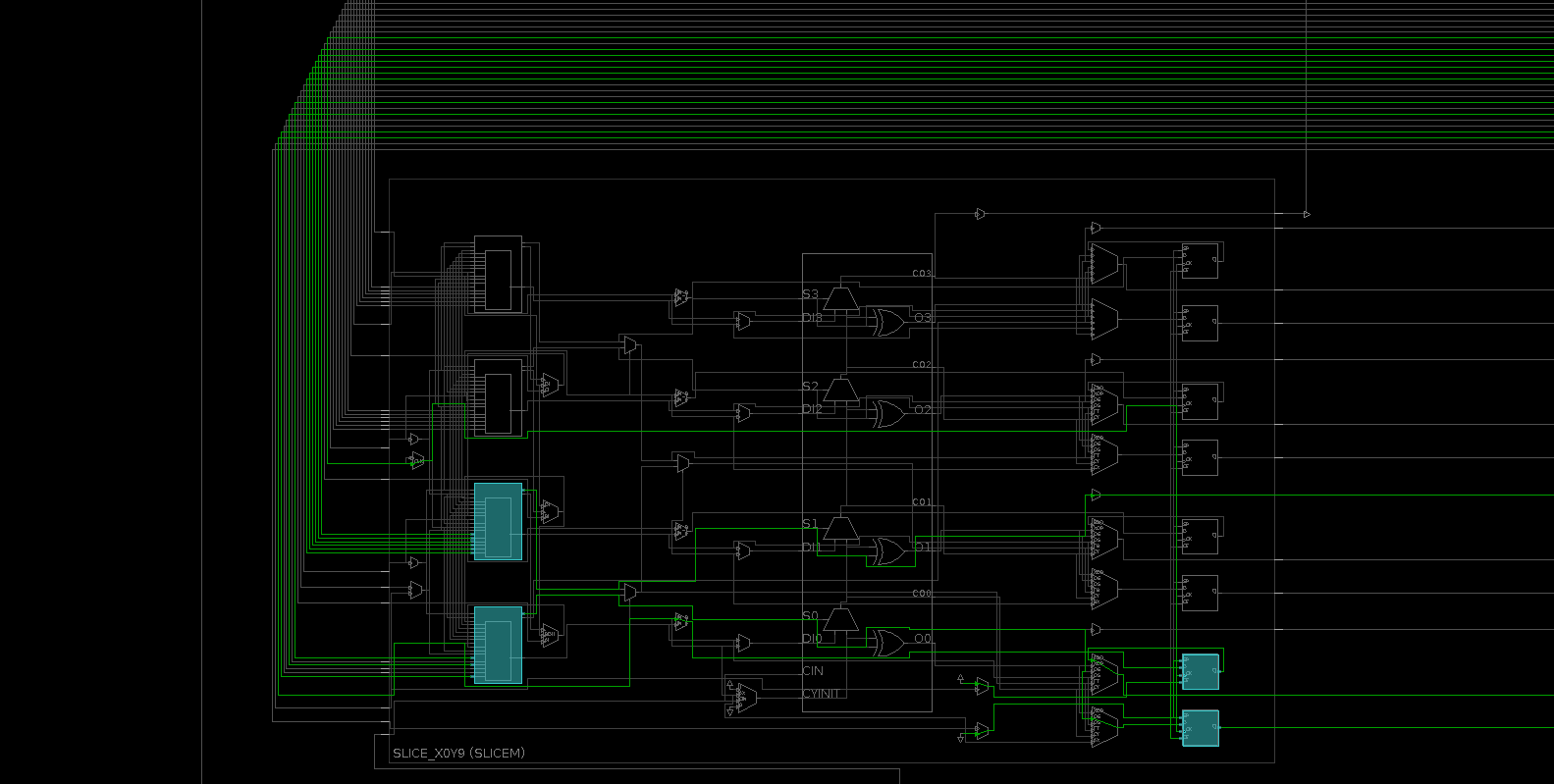

`default_nettype wireこの場合は次のようになりました。

ケース2に比べてLUTが1個減り、つぎの構成になりました。

だから、なんなのさぁと言われても何もないんですけどね。