さて、VitisをするためにUltra96V2のVitis 2020.1用 Platformを作成してみます。

基本的に@https://twitter.com/marsee101さんのブログを見るとよいです。

実行環境はつぎのとおりです。

git://github.com/aquaxis/ultra96v2_vivadoにVivado 2020.1で構築できるtclスクリプトを置いています。

次のようにBranchをv2020.1でcloneします。

$ git clone git://github.com/aquaxis/ultra96v2_vivado -b v2020.1cloneが完了したら次のようにディレクトリを移動して、Vivado 2020.1の環境を設定してからmakeを行うとVivadoプロジェクトを生成します。

makeを実行してVivadoプロジェクトができるまで少し時間がかかるのでコーヒーブレイクでもしておきましょう。

$ cd ultra96v2_vivado/

$ source /opt/Xilinx/Vitis/2020.1/settings64.sh

$ make create_designVivadoプロジェクトが生成されるとultra96v2というディレクトリが生成されています。

ultra96v2ディレクトリにultra96v2.xprがあるのでVivadoで開くと生成したUltra96V2のVivadoプロジェクトを確認することができます。

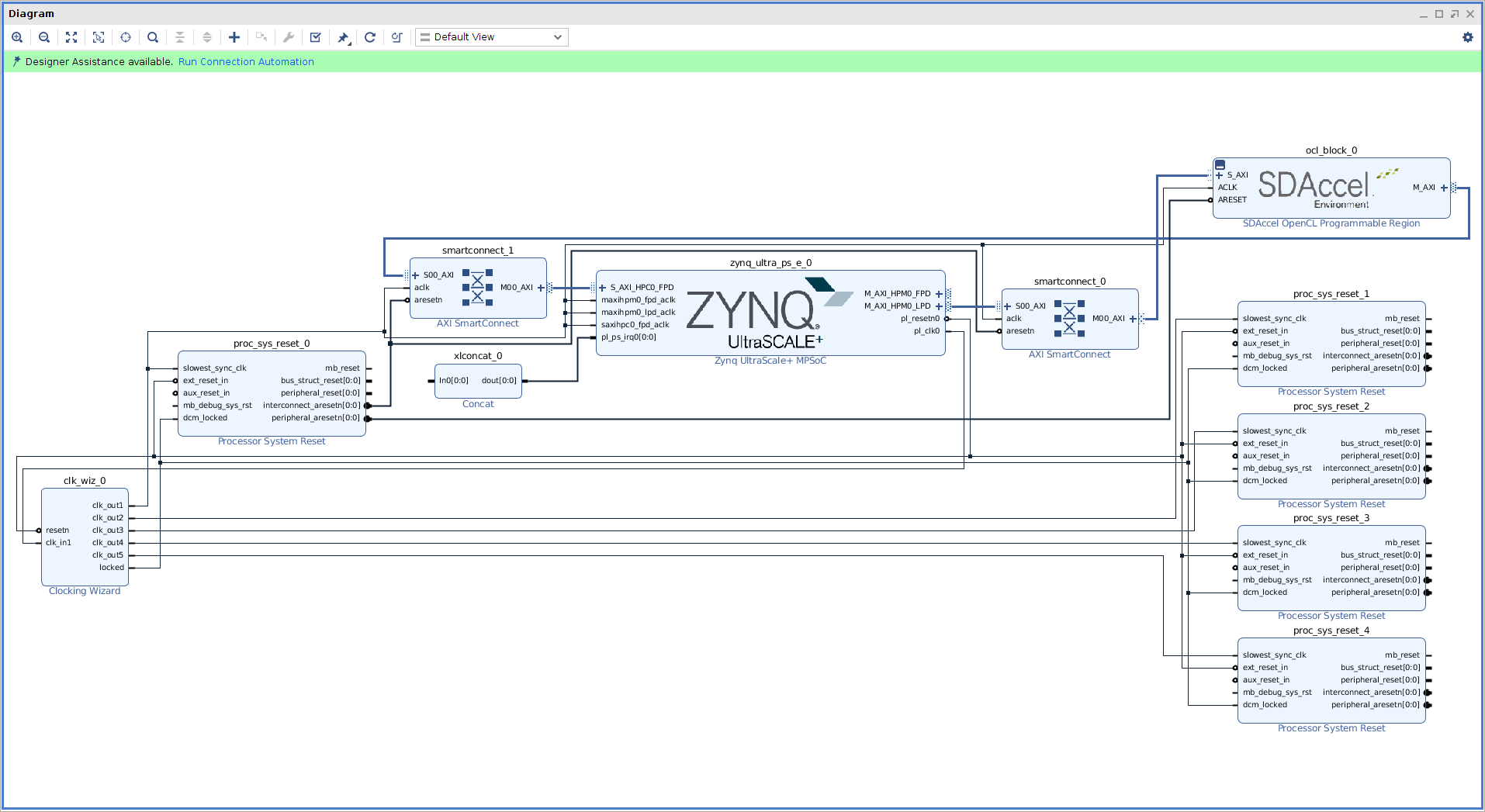

Vivadoプロジェクトを開いて、IP Intergatorを開くと次のようなブロック構成を確認することができます。

Vivadoプロジェクトを生成したMakefileを確認してみます。

Makefileは次のようになっています。

Vivadoプロジェクトを生成したのはcreate_designを実行しました。

他にcreate_fsbl、 create_dts、create_pfmがあり、FSBL(First Stage Boot Loader)、Device Tree、Hardware Platformを生成できるようにtclファイルを呼び出して実行するようにしています。

all: create_design create_fsbl download_dts create_dts

create_design:

vivado -mode batch -source create_design.tcl -log log_create_design.log

create_fsbl:

xsct create_fsbl.tcl

cp fsbl/executable.elf ./fsbl.elf

download_dts:

git clone https://github.com/Xilinx/device-tree-xlnx.git -b xilinx-v2020.1

create_dts:

xsct create_dts.tcl

create_pfm:

xsct create_pfm.tcl

clean:

rm -rf *.jou *.log *.str *.dcp *.mcs *.prm *.bit

rm -rf usage_*.html tight*.txt usage_statistics_webtalk.xml

rm -rf ultra96v2.xsa

rm -rf psu_init*

rm -rf hd_visual ultra96v2 xsa

rm -rf fsbl drivers

rm -rf dts device-tree-xlnx

rm -rf nohup.out

rm -rf ultra96v2_platform

rm -rf fsbl.elfVivadoプロジェクトがあれば、FSBLを生成することができます。

FSBLを生成する前にFSBLを生成時にVivado/Vitisがgmakeを使用するのでもし、linkを貼っていない場合は次のようにgmakeのlinkを作成します。

$ sudo ln -s /usr/bin/make /usr/bin/gmakeそして、make create_designを行ったディレクトリでそのまま次を実行します。

$ make create_fsblFSBLの生成が完了するとディレクトリにfsbl.elfができあがります。

FSBLはfsblというディレクトリでビルドされ、executable.elfというファイルで生成されます。

このファイルとディレクトリにあるfsbl.elfは同じファイルです。

DeviceTreeも生成できるようになっています。

ここで生成したDeviceTreeは使用していないのですが今後、ちゃんと使えるかどうか確認していく予定です。

今のところは独自に作成したDeviceTreeとの差分確認用に作成しています。

Device Treeの生成は次のように実行します。

$ make download_dts

$ make create_dtsまずはhttps://github.com/Xilinx/device-tree-xlnx.gitからDeviceTreeを生成するためのHeaderファイルなどをダウンロードします。

それからDeviceTreeを生成します。

DeviceTreeはdtsディレクトリに生成されます。

system-top.dtsから他のdtsiを参照しています。

次のようにdtcコマンドを実行するとdtbを生成できます。

$ dtc -I dts -O dtb -o system-top.dtb system-top.dtsMakefileにはcreate_pfmがあるのでPlatformを生成できることを予想しているでしょう。

Makefileを見て、make allのallのルールにどうしてcreate_pfmを入れていないんだとなんかあるのかな?と、気づいたかもしれません。

正解です。

VivadoプロジェクトだけではVitis用のPlatformを生成することはできません。

VitisのPlatformを生成するにはアプリケーション環境が必要になり、事前に用意しておかなければいけません。

そのためにallのルールからcreate_pfmを外しています。

とりわけ、ここではLinuxの話しかしないのでPetaLinuxやYocto ProjectのようなLinuxディストリビューションを用意しておく必要があるということです。

すでにPetaLinuxとかでLinuxディストリビューションを用意できていればcreate_pfm.tclを参考に修正して作成してみてくださいませ。

Vitis 2020.1用Platformでは下記の最低条件があります。

Clock Wizardを配置し、最低2つのClockを用意しておかなければいけない(チュートリアルは5つなので生成するプロジェクトを5つにしています)Processor System ResetをClockごとに用意するconcatを配置しておくVivado 2019.2まではClockはZynqのpl_clk0だけでも問題なくPlatformを生成できましたがVivado 2020.1ではこれでPlatformを生成するとVitisでxclbinを実行したときにエラーが発生します。

どうも、Vivado 2020.1ではデフォルトで2つのClockを使用するようにしたようですね。

おそらく、他の最低限の条件があると思われるので意味不明なエラーが発生した場合はチュートリアルので構成と比較すると良いでしょう。

VivadoプロジェクトのIP Integratorを修正した場合、Export → Export Block Designでsrc/system.tclに出力するとベースを保存しておくことができます。