VitisとはXilinx社のFPGA開発環境です。

これから2日おきペースぐらいでVitisを勉強していきたいと思います。

まずは開発環境を整えていきましょう。

筆者が使用しているOSはUbuntu 18.04.3 LTSです。

Vitisの現在リリースされているバージョンは2019.2です。

2019.2.1(Update 1)をダウンロードできますがRFSoCを有効にしているだけのようですのでほとんど人はインストールする必要がないでしょう。

Xilinx社のWebページから次のメニューを辿って、ダウンロードします。

Support → Downloads & Licensing

ダウンロードするにはユーザー登録が必要なので登録してからダウンロードします。

ダウンロードページを見ると5つのタブが有ります。

VivadoはVerilog HDLやVHDL、または高位合成を使用してFPGAを開発していくツールです。

Vitisはソフトウェア言語でFPGAを開発するツールです。

2019.1のときはVivado SDKとSDx(SDSoCとSDAccel)があったのですがこれらが統合されました。

今回のターゲットはコレです。

Vitis用のPlatformプロジェクトです。

Xilinx社で販売されている評価ボードのPlatformが用意されています。

Yocto ProjectをベースとしたZynq-7000、ZynqMPSoC、MicroBlaze向けの組込みLinuxディストリビューションを構築するフレームワークです。

Device ModelsはBSDLモデルをダウンロードすることができます。

BSDLはBoundary Scan Description Languageの略でピンの記述やI/Oピンが記述されたものです。

バウンダリ・スキャン・テスを作成する場合に使用されます。

ダウンロードできたらインストールするだけです。

インストールが完了するとインストール先に次のディレクトリを確認できます。

筆者のインストール先は/opt/Xilinxです。

/opt/Xilinx/DocNav /opt/Xilinx/Vitis /opt/Xilinx/Vivado /opt/Xilinx/xic

Boardfileとは評価ボードで必要なデバイスの設定やピン配置などがあらかじめ定義づけされているテンプレートです。

Boardfileをインストールしておくと最初からプロジェクトを構築する場合に便利です。

ダウンロードしたBoardfileは次のディレクトリにコピーします。

[インストールしたディレクトリ名]/Vivado/[バージョン]/data/boards/board_files/

私の場合は/opt/Xilinxにインストールするのでインストール先は/opt/Xilinx/Vivado/2019.2/data/boards/board_files/です。

Vitisを使用する場合は次のように環境設定を行います。

$ source /opt/Xilinx/Vitis/2019.2/settings64.shVivadoのみを使用する場合は次の様の環境設定を行います。

$ source /opt/Xilinx/Vivado/2019.2/settings64.shVitisの起動は次のように実行します。

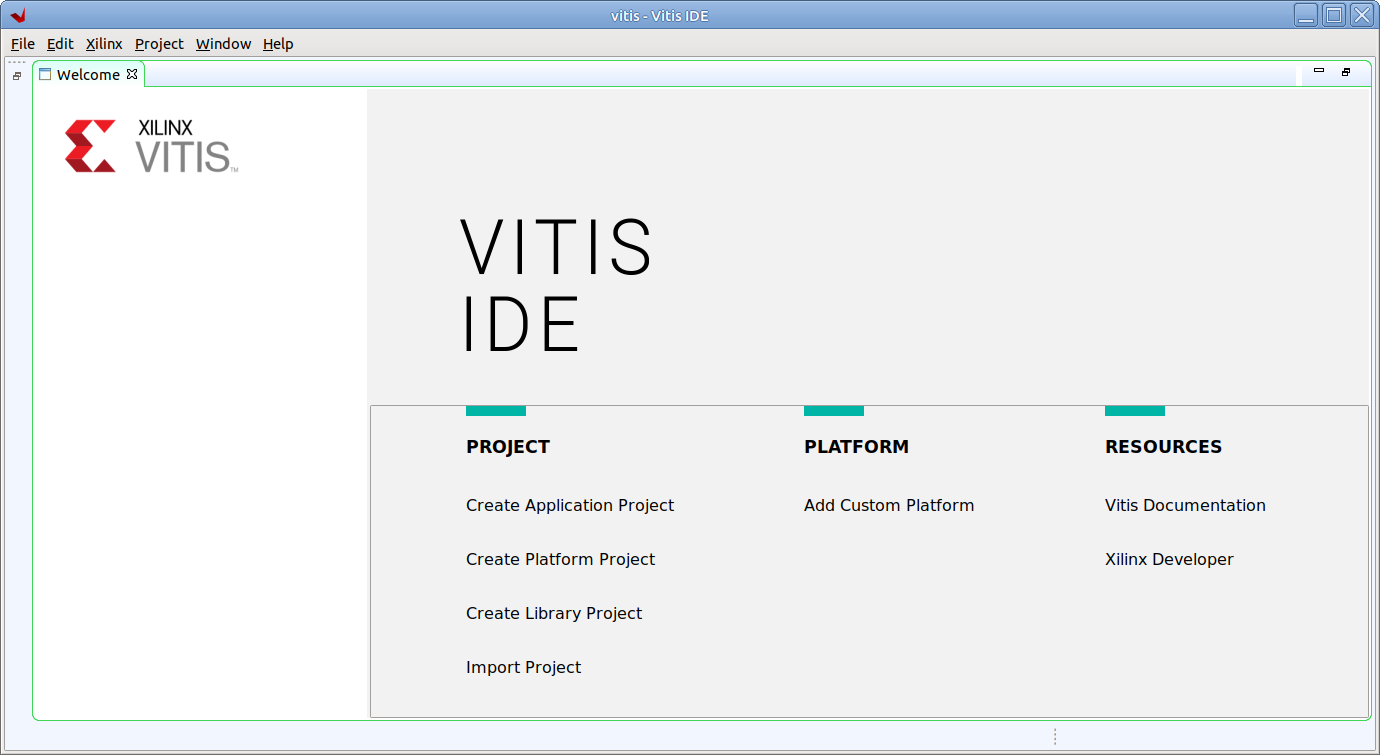

$ vitisこんなウィンドウが立ち上がるでしょう。

次回は「Vitisの使い方」を勉強しましょう。