v2019.2がリリースされたXilinxのツールですがSDSoCがVitisに統合されていることになっています。

実際にはSDSoCの使い勝手の環境は統合されておらず、PL層はOpenCLで制御するSDAccelの使い勝手が提供されるようになりました。

SDSoCが得手不得手は私が考えるに次の通りです。

このような感じだったのでSDSoC環境ではまずはアルゴリズムを考えてから関数分離をトライアンドエラーで性能のいいところを見つけていくということができました。

Vitisの得手不得手は私が考えるに次のとおりです。

Vitis環境の場合、CPUとFPGAを分離して開発するのであれば、私の場合はぶっちゃけRTLで書けば済むことなのでC言語とかソースコードで開発しなければいけないという観点に捕らわれる必要がなくなります。

SDSoC環境とVitis環境で一つ嫌な点があります。

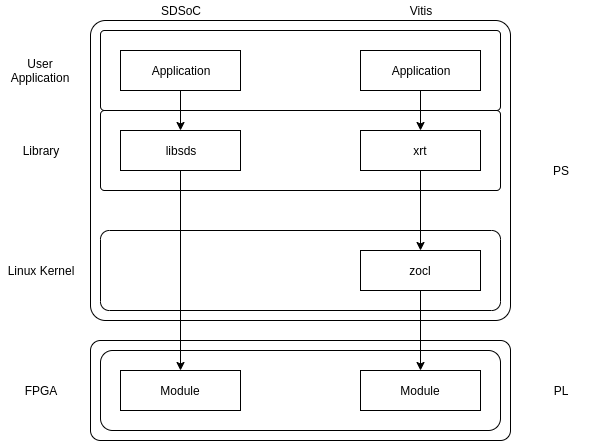

アプリケーションからFPGAへのアクセスが次の図のようになります。

SDSoC環境はFPGAへのアクセスはダイレクトにアクセスしていましたが、Vitis環境ではXRT→zoclを通じて、FPGAにアクセスします。

Linux Kernel層で主だった制御がないのにKernelドライバにアクセスしなければいけません。

これはKernelドライバを通すから性能云々というのではなく、Linux Kernelのバージョンを縛ってしまう状況が発生します。

また、xrtとxzolの依存関係も発生します。

もちろん、xrtとzoclが適切に最新のLinux Kernelに追従していれば特に問題は発生しません。

必要のないラッパーなどがあると、構成が複雑になるだけでなく不具合も発生しやすくなるので私としてはVitisの構成は好きではないです。

そして、SDSoC環境の場合はFPGAにダイレクトにアクセスできる環境を作れていたのでLinux Kernelのバージョンが変われば、例えば、新しいバージョンに置き換えることができました。

Vitis環境ではこれができなく、つまり、Linux Kernelの新しいバージョンなどを試しづらくなるのです。

常に新しいバージョンへ移行したいのは不具合観点からです。

今のところ、Xilinx社が積極的にLinux KernelのMainlineに関わっていってるように思えないので追従することはできないでしょう。

もう一つ、SDSoC環境であればFPGA化する関数はCPU側でも全く同じアクセス制御で使えるというのができなくなるのがちょっと残念です(このケース、ほとんどの人は使わないですが・・・)。