README.mdが長いのでぼちぼちと進めよう。

次のようにscripts/trd_prj.tclをVivadoで読み込み、起動します。

$ vivado -source scripts/trd_prj.tcl

****** Vivado v2020.2 (64-bit)

**** SW Build 3064766 on Wed Nov 18 09:12:47 MST 2020

**** IP Build 3064653 on Wed Nov 18 14:17:31 MST 2020

** Copyright 1986-2020 Xilinx, Inc. All Rights Reserved.

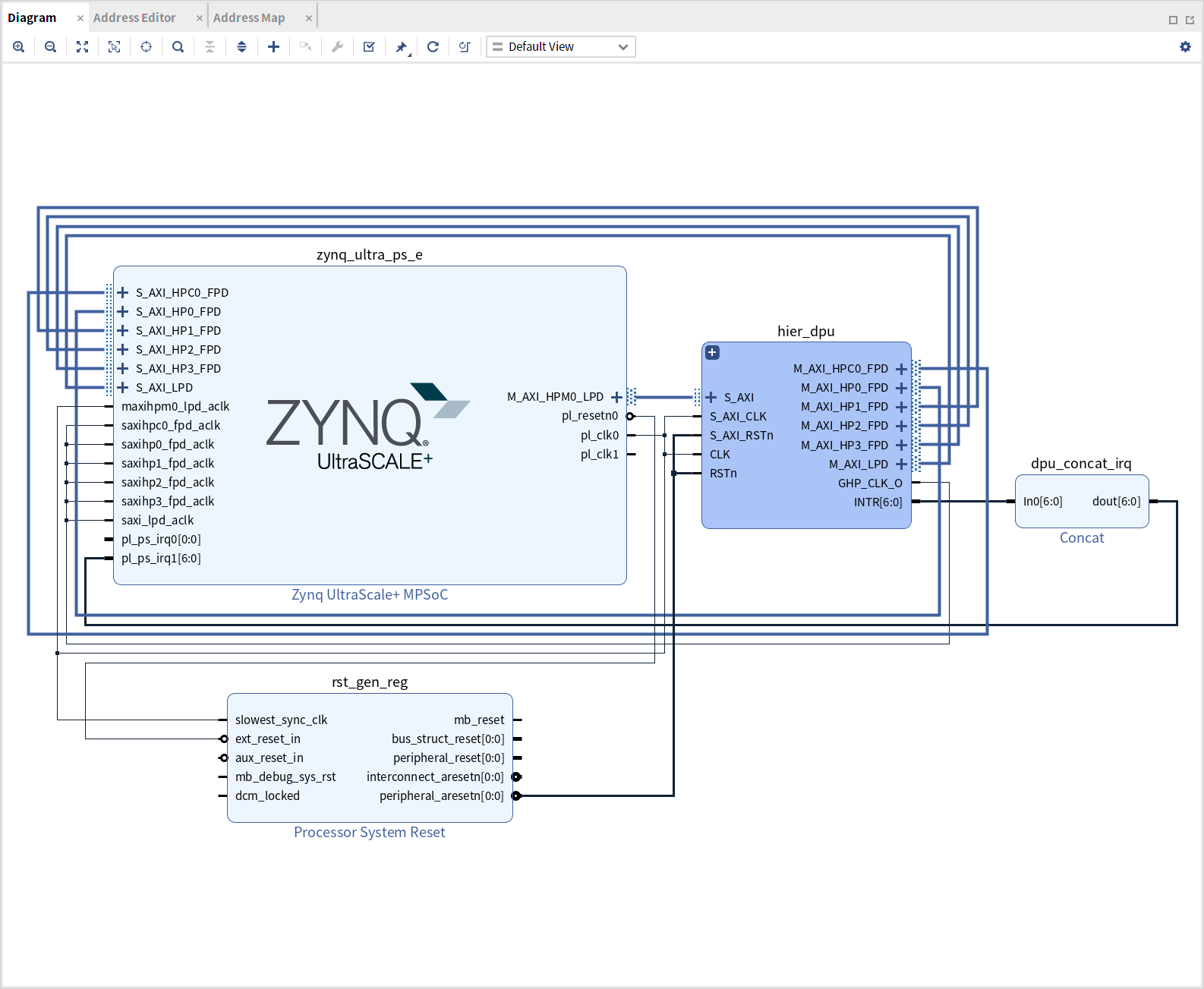

start_guiこんな感じにプロジェクトができた。

なんだ簡単やん。

なんか想像してたのと違うけど…

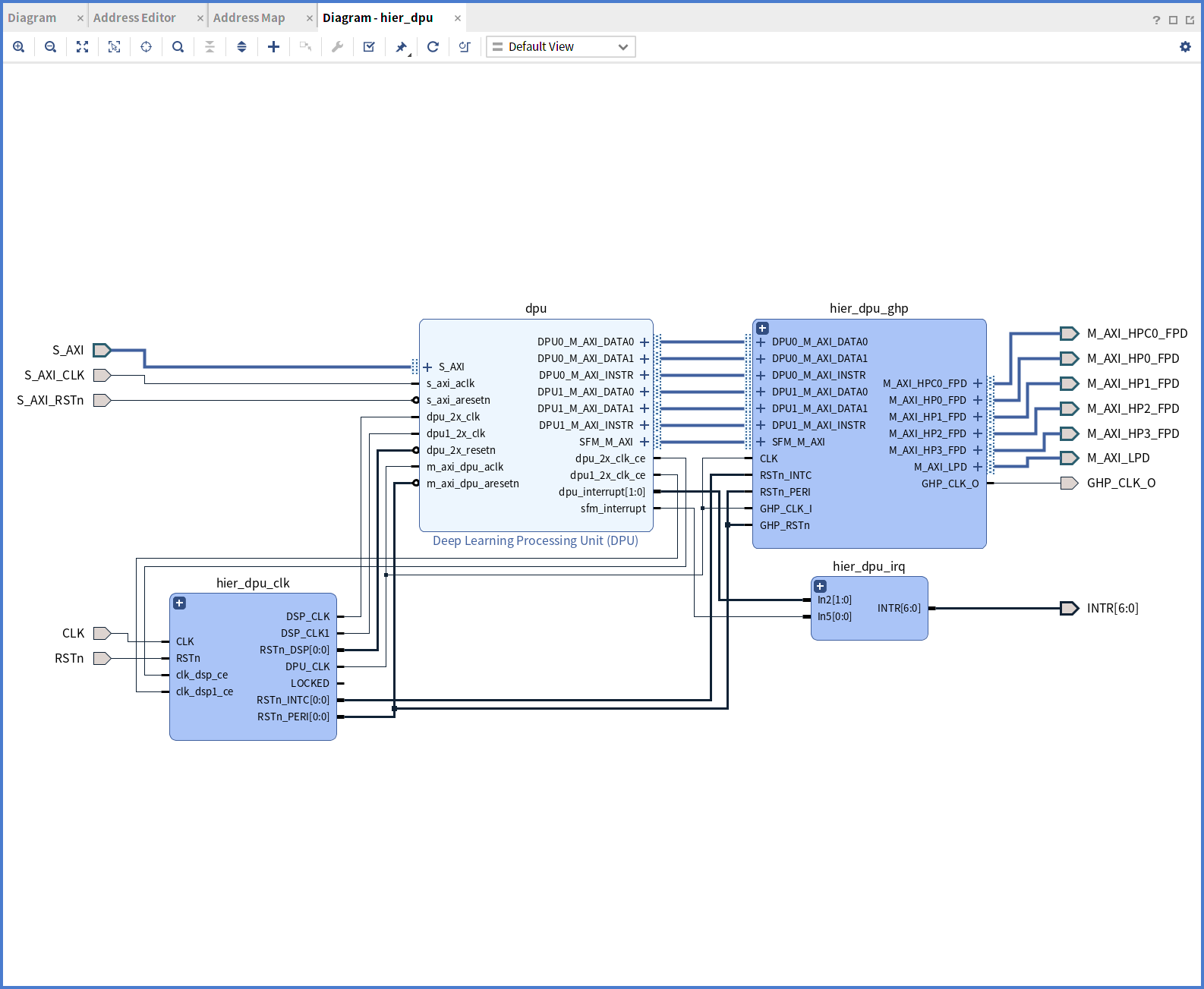

せっかくだから、hier_dpuの中身を見てみよう。

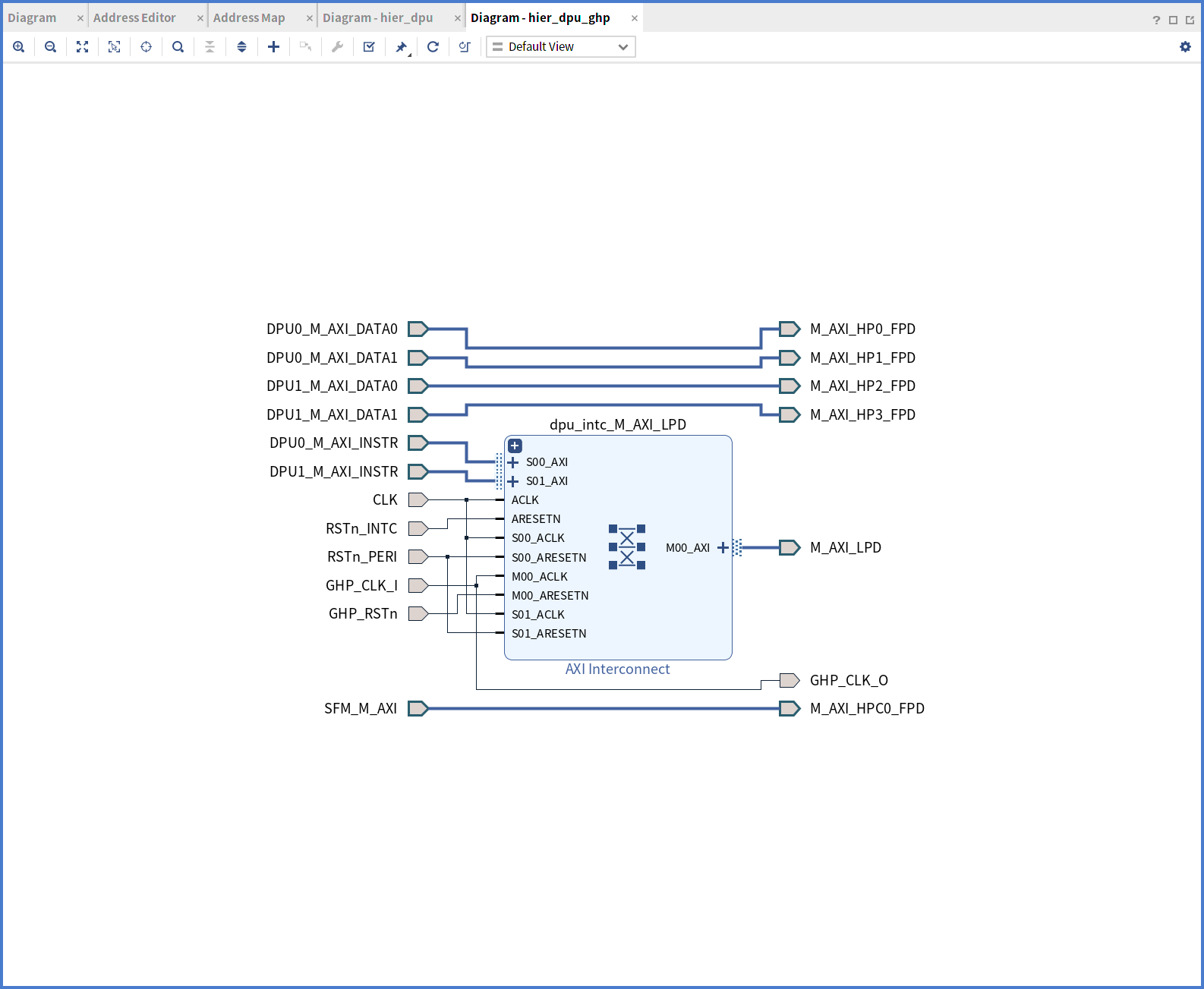

hier_dpu_dhpを覗いてみよう。

そぉ〜なってるのね。

あれ?

ZCU104で探してたつもりなのにZCU102でプロジェクトができてる。

ZCU104用はどういう風に作るんだろう?

それとも見つけたVivadoプロジェクトを間違えた?

VivadoプロジェクトはZCU102だけど、トップ階層を見ると信号がなかった。

デザインはチップ内で閉じているプロジェクトだったようだ。

つまり、ZCU102とZCU104の差分はないということと理解して良いのかな?

ZCU104で使う場合は単にPeojct deviceを変更すればいいだけかな?

ZCU104でtclファイルに限定すると次の3つが見つかる。

$ find ./|grep -i "zcu104.*\.tcl"

./Vitis-AI/dsa/DPU-TRD/prj/Vitis/syslink/zcu104_lowpower.tcl

./Vitis-AI/dsa/WAA-TRD/proj/build/classification-pre_DPUv2/syslink/zcu104_lowpower.tcl

./Vitis-AI/dsa/WAA-TRD/proj/build/detection-pre_DPUv2/syslink/zcu104_lowpower.tclこの3つのファイルの中身は同じだ。

ZCU104でVivadoプロジェクトを作成するときはこれらが使われるということなのか?

それとも、./Vitis-AI/dsa/DPU-TRD/prj/Vitis/syslink/zcu104_lowpower.tclがVitisで呼び出されてモジュールを構成されるということなんだろうか?

そういえば、ライブラリからどのモジュールを制御しているのか確認してなかったな。

明日はライブラリに戻ってみるかな?

Tweet write: 2021/01/15/ 00:00:00